集成電路封裝中的EDA玩家們 設計、仿真與創新的前沿探索

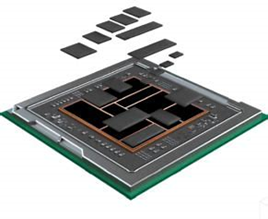

集成電路封裝是電子設計自動化(EDA)領域中的重要環節,它不僅關乎芯片性能的最終實現,還深刻影響著產品的可靠性、功耗和成本。隨著摩爾定律的逼近物理極限,先進封裝技術如2.5D/3D集成、系統級封裝(SiP)和扇出型晶圓級封裝(FOWLP)正成為行業焦點,EDA工具在這一變革中扮演著關鍵角色。

在集成電路設計的早期階段,EDA工具已介入封裝規劃。設計師利用工具進行芯片與封裝協同設計,確保信號完整性、電源完整性和熱管理。例如,Cadence的Allegro Package Designer和Synopsys的3D-IC Compiler支持多芯片模塊的布局和互連優化,幫助用戶在虛擬環境中驗證封裝方案,減少物理原型迭代。

仿真與分析是EDA玩家的核心戰場。ANSYS的HFSS和SIwave工具專注于電磁仿真,解決高頻信號在封裝中的傳輸損耗和串擾問題;Mentor(現為Siemens EDA)的Calibre用于物理驗證,確保封裝設計符合制造規則。這些工具通過機器學習增強,能快速預測熱應力和機械應力,防止芯片在封裝過程中失效。

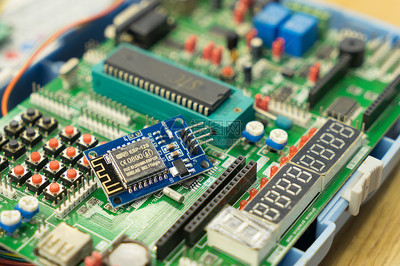

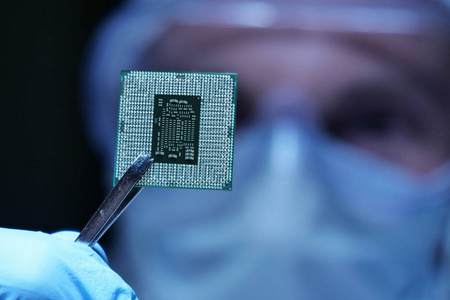

EDA玩家還推動著封裝創新。以臺積電的CoWoS和Intel的Foveros為例,EDA平臺整合了芯片、中介層和基板的設計流程,實現異構集成。新興的EDA公司如Zuken和Keysight也加入競爭,提供針對汽車電子和物聯網的定制化封裝解決方案。

挑戰依然存在。封裝復雜度增加導致設計周期延長,EDA工具需更智能的自動化功能;供應鏈波動和成本壓力要求工具支持多物理場協同優化。未來,EDA玩家將聚焦于AI驅動設計、云平臺協作和可持續發展,助力集成電路封裝邁向更高集成度和能效。

EDA工具是集成電路封裝的“大腦”,從設計到制造的全流程中,它們連接著創新與現實。隨著5G、人工智能和自動駕駛的興起,EDA玩家們將繼續引領封裝技術革命,塑造電子產業的明天。

如若轉載,請注明出處:http://www.y1672.cn/product/13.html

更新時間:2026-01-20 06:50:12