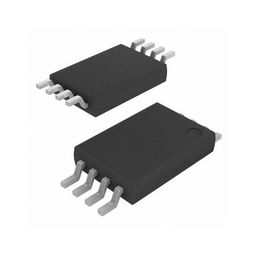

時鐘緩沖器NB3N2304NZDTG 高性能集成電路設計的關鍵驅動器

在高速數字系統和通信設備中,時鐘信號的完整性、穩定性和低抖動是確保系統性能的基石。時鐘緩沖器作為時鐘樹設計中的核心組件,其作用至關重要。美國安森美半導體(ON Semiconductor)推出的NB3N2304NZDTG便是一款專為高性能應用設計的LVCMOS/LVTTL時鐘緩沖器/驅動器集成電路,它在現代集成電路設計中扮演著驅動與分配精準時鐘的關鍵角色。

一、 器件概述與核心特性

NB3N2304NZDTG是一款1:4的差分至LVCMOS/LVTTL時鐘緩沖器。其核心功能是接收一個差分或單端輸入時鐘信號,并將其轉換為四路低電壓、低抖動的CMOS/TTL電平輸出。該器件設計用于滿足高頻、低相位噪聲和低功耗的應用需求,典型工作頻率可達200MHz以上。其主要特性包括:

- 低附加抖動:在優化時鐘信號質量時,器件自身引入的抖動極低,這對于高速SerDes(串行器/解串器)、FPGA、網絡處理器和測試測量設備的時序預算至關重要。

- 靈活的電源電壓:支持3.3V或2.5V的VCC供電,輸出可與1.8V、2.5V或3.3V的LVCMOS/LVTTL電平兼容,提供了出色的系統集成靈活性。

- 差分或單端輸入:輸入級設計既能接受LVPECL、LVDS或CML等差分信號,也能接收單端CMOS/TTL信號,通過內部偏置電路實現自動適配,簡化了前端接口設計。

- 輸出使能(OE)功能:集成的輸出使能引腳允許用戶將所有輸出置于高阻態,便于電源管理和測試,有助于降低系統總功耗。

- 小型化封裝:通常采用節省空間的TSSOP-16或類似封裝,符合現代電子設備高密度PCB布局的要求。

二、 在集成電路與系統設計中的關鍵作用

在復雜的片上系統(SoC)或電路板設計中,NB3N2304NZDTG作為專用時鐘驅動器,解決了以下幾個關鍵設計挑戰:

1. 時鐘扇出與負載驅動

現代處理器、FPGA或ASIC通常需要將同一個參考時鐘分配給多個負載。直接驅動可能導致時鐘信號衰減、邊沿速率下降和時序偏移。NB3N2304NZDTG提供了強大的輸出驅動能力,能夠驅動多達四個重負載,同時保持信號邊沿陡峭,確保所有接收端時鐘的一致性。

2. 信號電平轉換與接口橋接

系統中常常存在不同電壓域的器件。該緩沖器能夠將來自時鐘發生器(可能是LVPECL電平)的信號,干凈、高效地轉換為后端芯片所需的LVCMOS電平,充當了可靠的信號電平轉換器和接口橋梁。

3. 改善信號完整性與減少抖動

時鐘路徑上的傳輸線效應、反射和串擾會劣化信號質量。NB3N2304NZDTG具有快速上升/下降時間和良好的輸出對稱性,能夠重塑時鐘波形,抑制振鈴,并通過其低抖動特性有效凈化時鐘,為高速數據轉換和傳輸提供純凈的時序參考。

4. 時鐘樹綜合與延時管理

雖然它本身不是可編程延時線,但其各輸出通道間極低的輸出到輸出偏移(Skew)特性,對于構建平衡的時鐘分配網絡至關重要。設計師可以依賴其一致的性能來最小化時鐘到達不同端點的時序差異。

三、 設計考量與應用領域

在采用NB3N2304NZDTG進行設計時,工程師需重點關注:

- 電源去耦:必須在電源引腳附近布置高質量的去耦電容(通常為0.1μF和0.01μF并聯),以濾除噪聲,保證電源完整性,這是實現低抖動性能的前提。

- PCB布局與阻抗匹配:輸入和輸出走線應作為受控阻抗傳輸線來處理,尤其是差分輸入對,需保持等長、等距,并做好終端匹配,以最小化反射。

- 熱管理:雖然功耗相對較低,但在高環境溫度或全速運行下,仍需考慮其熱耗散,確保結溫在安全范圍內。

其典型應用領域廣泛,包括但不限于:

- 網絡與通信設備:路由器、交換機、光纖通道卡中的時鐘分配。

- 計算與存儲:服務器主板、RAID控制器、高速背板。

- 工業與測試儀器:高性能示波器、信號發生器、自動化測試設備(ATE)。

- 消費電子:高端數字電視、機頂盒、A/V接收機中需要高質量時鐘的部分。

結論

NB3N2304NZDTG時鐘緩沖器驅動器代表了高性能時鐘管理集成電路的一個成熟解決方案。它通過精心的內部電路設計——包括高性能的差分輸入接收器、低噪聲的放大驅動級以及穩定的偏置與電源管理電路——將時鐘分配任務專業化、集成化。在追求更高數據速率和更嚴格時序余量的今天,此類器件的正確選型與應用,直接關系到整個數字系統能否穩定可靠地運行于性能巔峰,是集成電路與系統設計師手中不可或缺的關鍵棋子。

如若轉載,請注明出處:http://www.y1672.cn/product/64.html

更新時間:2026-01-18 02:26:24