微型晶體管計(jì)算機(jī)的集成電路設(shè)計(jì)

隨著信息技術(shù)的飛速發(fā)展,微型晶體管計(jì)算機(jī)已成為現(xiàn)代電子設(shè)備的核心,其高性能和小型化依賴于集成電路(IC)設(shè)計(jì)的創(chuàng)新。集成電路設(shè)計(jì)是電子工程的關(guān)鍵領(lǐng)域,涉及將數(shù)百萬甚至數(shù)十億個(gè)微型晶體管集成到單一芯片上,以實(shí)現(xiàn)計(jì)算、存儲(chǔ)和控制功能。本文將探討微型晶體管計(jì)算機(jī)中集成電路設(shè)計(jì)的基礎(chǔ)原理、關(guān)鍵技術(shù)和應(yīng)用前景。

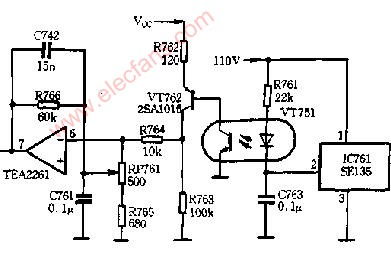

集成電路設(shè)計(jì)的基礎(chǔ)始于晶體管技術(shù)的演進(jìn)。晶體管作為電子開關(guān),是計(jì)算機(jī)邏輯運(yùn)算的基本單元。從早期的雙極型晶體管到現(xiàn)代金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET),晶體管的微型化使得芯片集成度大幅提升。設(shè)計(jì)過程通常包括系統(tǒng)架構(gòu)規(guī)劃、邏輯設(shè)計(jì)、電路仿真和物理布局。設(shè)計(jì)師使用硬件描述語言(如Verilog或VHDL)定義電路功能,并通過電子設(shè)計(jì)自動(dòng)化(EDA)工具進(jìn)行仿真和優(yōu)化,確保電路在功耗、速度和面積之間達(dá)到平衡。

在微型晶體管計(jì)算機(jī)中,集成電路設(shè)計(jì)面臨的主要挑戰(zhàn)包括功耗管理、散熱問題和信號(hào)完整性。例如,隨著晶體管尺寸縮小至納米級(jí)別,漏電流和熱效應(yīng)可能影響性能,設(shè)計(jì)師需采用低功耗設(shè)計(jì)技術(shù),如多閾值電壓和時(shí)鐘門控。3D集成電路和片上系統(tǒng)(SoC)的興起,允許將處理器、內(nèi)存和外圍接口集成于單一芯片,提升了計(jì)算效率并減小了設(shè)備體積。

應(yīng)用方面,微型晶體管計(jì)算機(jī)的集成電路廣泛應(yīng)用于智能手機(jī)、物聯(lián)網(wǎng)設(shè)備、醫(yī)療儀器和人工智能系統(tǒng)。隨著量子計(jì)算和神經(jīng)形態(tài)計(jì)算的發(fā)展,集成電路設(shè)計(jì)將探索新材料和架構(gòu),以突破傳統(tǒng)硅基技術(shù)的極限。集成電路設(shè)計(jì)是推動(dòng)微型晶體管計(jì)算機(jī)進(jìn)步的核心動(dòng)力,其創(chuàng)新將持續(xù)驅(qū)動(dòng)數(shù)字時(shí)代的變革。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.y1672.cn/product/34.html

更新時(shí)間:2026-01-18 15:45:51